欢迎来到贝博BB官网(中国)有限公司官网官方网站!

CMOS 数字隔离器系统应考虑事项有哪些?

2021-11-25 来源:

贝博BB官网(中国)有限公司官网

无论采用何种方式,隔离器都必须满足可靠电流隔离的安全标准。它们还必须足够可靠,能够比安装它们的设备更耐用,而在工业世界,这可能意味着要使用几十年。设计人员必须确保隔离电路能够承受可能导致物理损坏的电应力,并拒绝来自任何数量来源的破坏数据的噪声。因此,设计者必须仔细考虑关键隔离器操作参数,例如共模瞬态抗扰度、关键定时参数,例如传播延迟和脉宽失真,以及场相关规范,如EMI和RF敏感性。同样,连续工作电压和平均故障时间(MTTF)也是设备使用寿命的重要指标。

高压绝缘可靠性

绝缘可靠性直接影响隔离器防止用户暴露在高压下的能力,并且至关重要。绝缘体是隔离屏障的“心脏”,是维持系统安全的关键。绝缘必须均匀,没有可能导致局部击穿的空隙,这一点非常重要。绝缘体均匀性是绝缘体材料和制造工艺的函数。

由于在制造过程中产生的空隙,光耦的注塑塑料化合物的介电强度变化可达300%。相比之下,CMOS数字隔离器使用半导体氧化物层作为其主绝缘体。CMOS氧化物沉积工艺控制非常严格且高度均匀,由此产生的介电强度变化仅为20%。每个氧化层的击穿电压为每微米500 VACRMS(百万分之一米)。在晶圆制造过程中,通过简单地堆叠氧化层来实现更高的电压(例如5 kVACMs)。其结果是,与独立于封装工艺的光耦和绝缘体可靠性相比,在更小的尺寸内获得更高的绝对最大击穿电压。

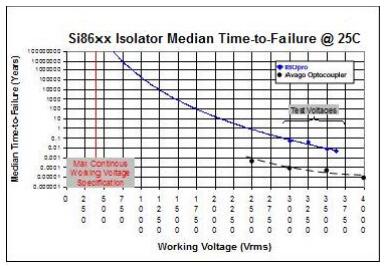

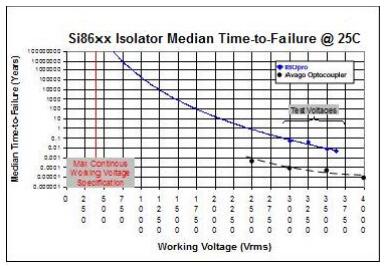

图片中,比较了CMOS数字隔离器与光耦的平均失效时间。这两种装置在相同的设备和相同的条件下进行测量。如图所示,2.5 kVACMS、6通道CMOS数字隔离器的外推中位失效时间在25°C温度和500 VDC电压下趋于1x108年。

图片中,比较了CMOS数字隔离器与光耦的平均失效时间。这两种装置在相同的设备和相同的条件下进行测量。如图所示,2.5 kVACMS、6通道CMOS数字隔离器的外推中位失效时间在25°C温度和500 VDC电压下趋于1x108年。

高压绝缘可靠性

绝缘可靠性直接影响隔离器防止用户暴露在高压下的能力,并且至关重要。绝缘体是隔离屏障的“心脏”,是维持系统安全的关键。绝缘必须均匀,没有可能导致局部击穿的空隙,这一点非常重要。绝缘体均匀性是绝缘体材料和制造工艺的函数。

由于在制造过程中产生的空隙,光耦的注塑塑料化合物的介电强度变化可达300%。相比之下,CMOS数字隔离器使用半导体氧化物层作为其主绝缘体。CMOS氧化物沉积工艺控制非常严格且高度均匀,由此产生的介电强度变化仅为20%。每个氧化层的击穿电压为每微米500 VACRMS(百万分之一米)。在晶圆制造过程中,通过简单地堆叠氧化层来实现更高的电压(例如5 kVACMs)。其结果是,与独立于封装工艺的光耦和绝缘体可靠性相比,在更小的尺寸内获得更高的绝对最大击穿电压。