欢迎来到贝博BB官网(中国)有限公司官网官方网站!

数字隔离器设计指南2

2022-02-15 来源:

贝博BB官网(中国)有限公司官网

4 PCB设计指南

4.1 PCB材料

对于工作速度低于150 Mbps(或上升和下降时间高于1 ns)且迹线长度高达10英寸的数字电路板,使用标准FR-4环氧玻璃作为印刷电路板(PCB)材料。FR-4(阻燃剂4)符合美国保险商实验室UL94-V0的要求,由于其在高频下较低的介电损耗、较少的吸湿性、较大的强度和刚度,以及其自熄性、易燃性,因此优于较便宜的替代品。

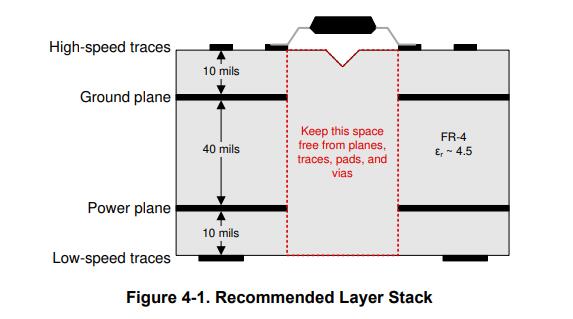

4.2层堆栈

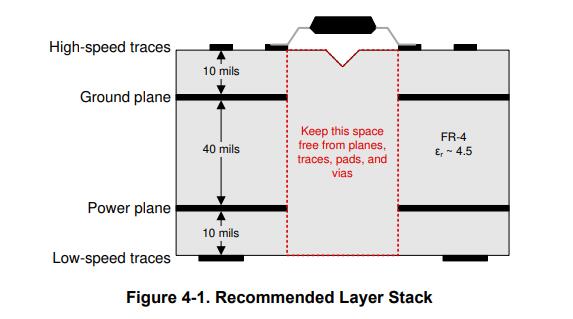

完成低EMI PCB设计至少需要四层(见图4-1)。层堆叠必须按照以下顺序(从上到下):高速信号层、地平面、电源平面和低频信号层。

●在顶层布线高速记录道可避免使用过孔(以及引入其电感),并允许在隔离器和数据链路的发射器和接收器电路之间进行干净的互连。

●在顶层布线高速记录道可避免使用过孔(以及引入其电感),并允许在隔离器和数据链路的发射器和接收器电路之间进行干净的互连。

●在高速信号层旁边放置一个实心接地层,为传输线互连建立受控阻抗,并为回流提供良好的低电感路径。

●将电源板放置在接地层旁边会产生约100 pF/in2的额外高频旁路电容。

●在底层路由较慢的速度控制信号允许更大的灵活性,因为这些信号链路通常有容限来容忍不连续性,如过孔。

如果需要额外的电源电压平面或信号层,请在堆栈中添加第二个电源/接地平面系统以保持对称。 这使得堆栈机械稳定并防止其翘曲。 此外,每个电源系统的电源层和接地层可以放置得更近,从而显着增加高频旁路电容。

4.3爬电距离

爬电距离是沿绝缘表面测量的两个导电部件之间的最短路径。适当的爬电距离可防止跟踪,这是一种由于绝缘表面上或附近的放电而在绝缘材料表面产生局部劣化的部分导电路径的过程。

漏电起痕的程度取决于材料的比较漏电起痕指数(CTI)和环境污染程度。 CTI 用于电绝缘材料,提供在标准测试期间通过跟踪导致失效的电压数值。 IEC 112 对跟踪和 CTI 提供了更全面的解释。

跟踪损坏绝缘材料通常是由于以下一个或多个原因造成的:大气湿度、污染、腐蚀性化学品和设备运行的海拔高度。

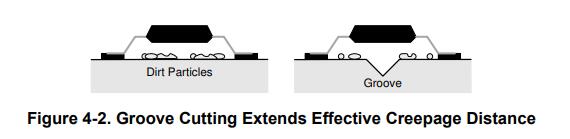

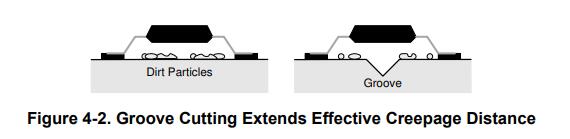

随着隔离电压水平的不断升高,拥有一个稳健的PCB设计比以往任何时候都更加重要,该设计不仅可以减少电磁干扰发射,还可以减少爬电问题。除了宽隔离器封装外,还可以使用槽等技术来达到所需的爬电距离(见图4-2)。

对于凹槽(>1 mm 宽),唯一的深度要求是现有爬电距离加上凹槽的宽度和两倍的凹槽深度必须等于或超过所需的爬电距离。 凹槽不得将基材削弱到不能满足机械测试要求的程度。

对于凹槽(>1 mm 宽),唯一的深度要求是现有爬电距离加上凹槽的宽度和两倍的凹槽深度必须等于或超过所需的爬电距离。 凹槽不得将基材削弱到不能满足机械测试要求的程度。

此外,在所有层上,保持隔离器下方的空间没有走线、过孔和焊盘,以保持最大爬电距离(见图 4-1)。

4.4受控阻抗传输线

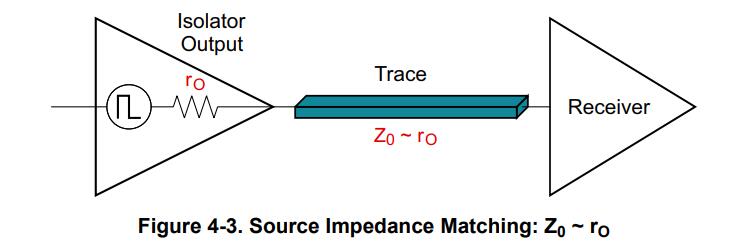

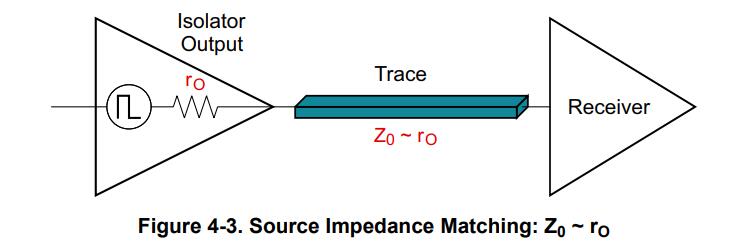

受控阻抗传输线是一条其特性阻抗Z0由迹线几何形状严格控制的迹线。通常,这些迹线与传输介质(如电缆和线路终端)的差分阻抗匹配,以最小化信号反射。在数字隔离器周围,受控阻抗迹线必须与隔离器输出阻抗Z0~rO匹配,这称为源阻抗匹配。

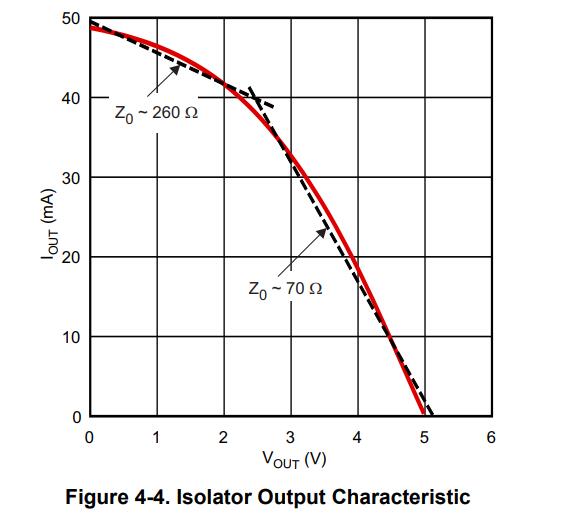

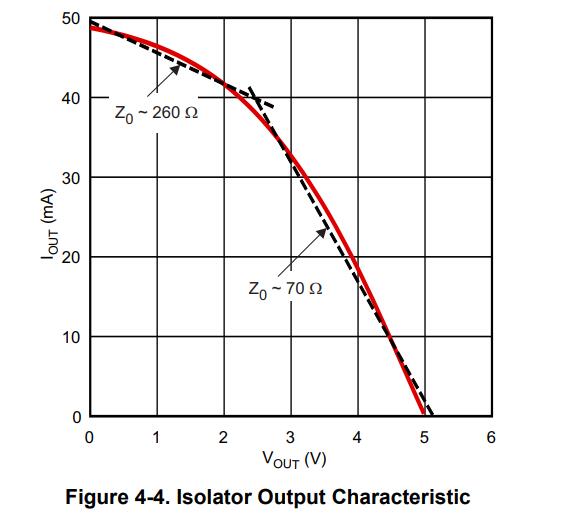

为了确定Z0,需要确定隔离器的动态输出阻抗rO=ΔVOUT/ΔIOUT。为此,图4-4(取自ISO7240数据表)中的输出特性由两个表示rO~260的线性段近似Ω 在低电压下,而对于大多数曲线(以及输出的过渡区),rO~70Ω。

为了确定Z0,需要确定隔离器的动态输出阻抗rO=ΔVOUT/ΔIOUT。为此,图4-4(取自ISO7240数据表)中的输出特性由两个表示rO~260的线性段近似Ω 在低电压下,而对于大多数曲线(以及输出的过渡区),rO~70Ω。

所需的迹线几何形状,如迹线厚度(t)和宽度(w)、迹线与相邻接地层之间的距离(d)以及PCB电介质(εr),部分取决于电路板制造工艺的镀铜能力和所选电路板材料的电介质。典型值为1盎司和2盎司镀铜,导致痕迹厚度分别为t=1.37密耳和t=2.74密耳。对于微带,FR-4环氧玻璃的介电值在εr=2.8到4.5之间变化,对于带状线迹线,介电值在εr=4.5之间变化。

所需的迹线几何形状,如迹线厚度(t)和宽度(w)、迹线与相邻接地层之间的距离(d)以及PCB电介质(εr),部分取决于电路板制造工艺的镀铜能力和所选电路板材料的电介质。典型值为1盎司和2盎司镀铜,导致痕迹厚度分别为t=1.37密耳和t=2.74密耳。对于微带,FR-4环氧玻璃的介电值在εr=2.8到4.5之间变化,对于带状线迹线,介电值在εr=4.5之间变化。

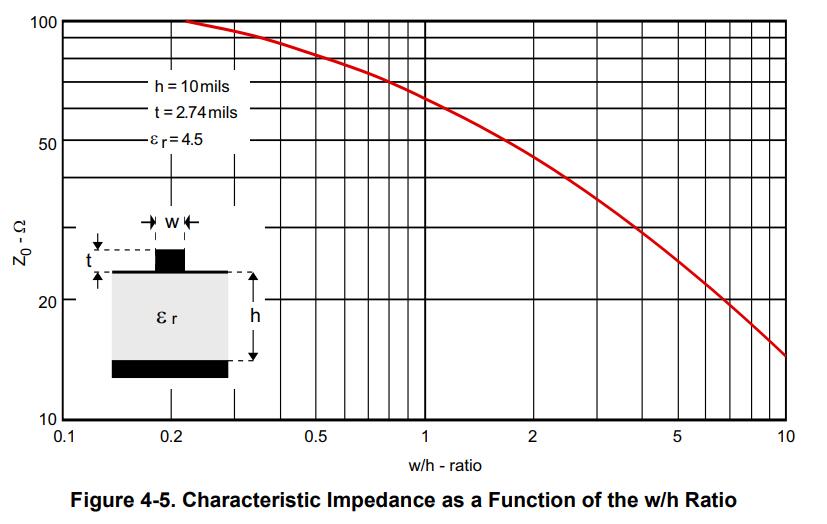

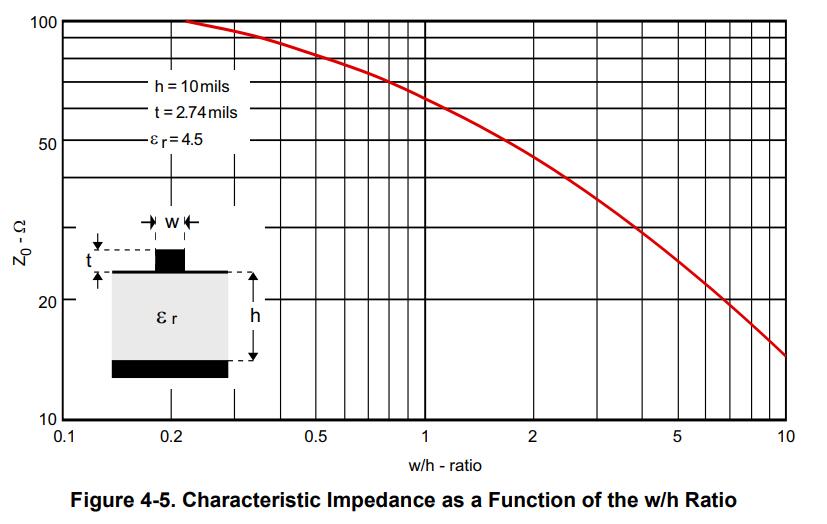

在给定t和εr的情况下,设计师可以通过迹线宽度w和距离d自由定义Z0。然而,对于PCB设计,最关键的尺寸不是w和d的绝对值,而是它们的比值w/d。简化设计师的任务,图4-5绘制了特征迹线阻抗,作为迹线厚度为2.74密耳(2-oz镀铜)、FR-4电介质为4.5以及高于接地层的迹线高度为10密耳时的宽高比(w/h)的函数。

从图4-5可以明显看出,70-Ω 设计要求水灰比约为0.8。如以下章节“基准面”中所述,设计低EMI板需要信号迹线和接地层之间紧密的电耦合,这是通过确保h=10密耳来实现的。因此,相应的记录道宽度为8密耳。必须在整个记录道长度上保持此宽度。否则,迹线宽度的变化会导致特性阻抗不连续,从而导致反射和EMI增加。

从图4-5可以明显看出,70-Ω 设计要求水灰比约为0.8。如以下章节“基准面”中所述,设计低EMI板需要信号迹线和接地层之间紧密的电耦合,这是通过确保h=10密耳来实现的。因此,相应的记录道宽度为8密耳。必须在整个记录道长度上保持此宽度。否则,迹线宽度的变化会导致特性阻抗不连续,从而导致反射和EMI增加。

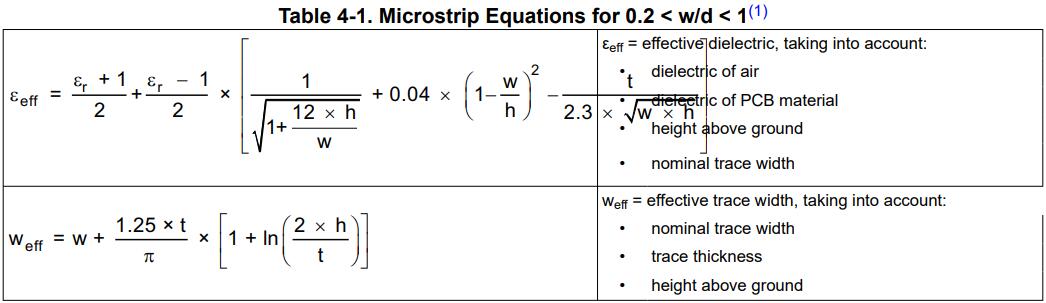

注意,前面的设计示例只是实现所需Z0的多种可能性之一。由于镀铜量较高或较低,或者可以使用不同的PCB材料,所以痕迹厚度不同,但需要改变w/d比。表4-1给出了计算特性阻抗Z0的相当复杂的数学方程,同时考虑了迹线厚度、宽度和电介质。

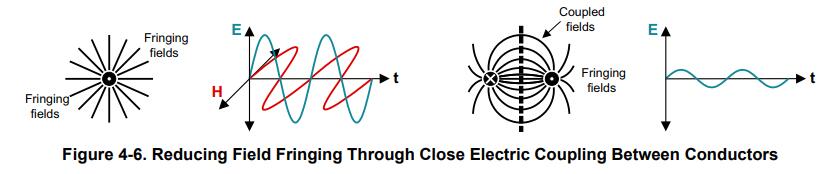

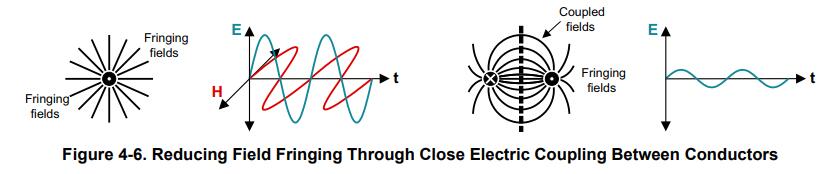

现在想象一下靠近的第二个导体,承载着等幅但极性相反的电流。在这种情况下,导体的相反磁场相互抵消,而它们的电场紧密耦合。两个导体的 TEM 波现在被剥夺了磁场,无法辐射到环境中。只有更小的边缘场可能能够耦合到外部,从而显着降低 EMI。

现在想象一下靠近的第二个导体,承载着等幅但极性相反的电流。在这种情况下,导体的相反磁场相互抵消,而它们的电场紧密耦合。两个导体的 TEM 波现在被剥夺了磁场,无法辐射到环境中。只有更小的边缘场可能能够耦合到外部,从而显着降低 EMI。

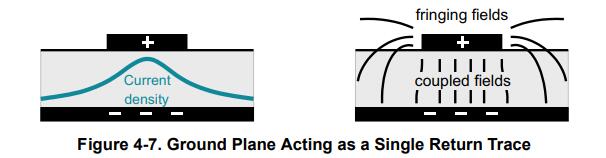

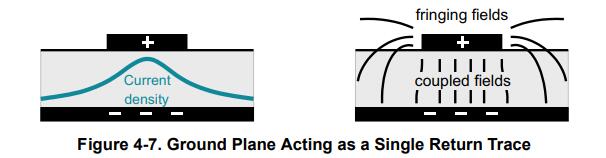

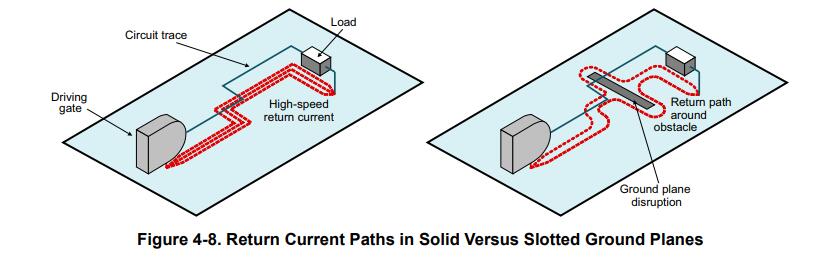

图 4-7 显示了在接地层和紧密耦合的信号走线之间发生的相同效应。高频电流遵循电感最小的路径,而不是阻抗最小的路径。由于电感最小的返回路径直接位于信号迹线下方,因此返回信号电流往往会沿着这条路径流动。受限的回流电流在接地层中形成了一个高电流密度区域,就在信号迹线的正下方。然后,该接地平面区域充当单个返回迹线,允许磁场抵消,同时为上方的信号迹线提供紧密的电耦合。

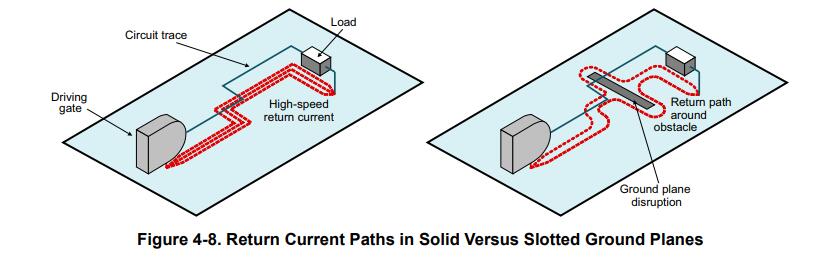

为了为返回电流提供连续的低阻抗路径,参考平面(电源和接地平面)必须是实心铜片,并且没有空隙和裂缝。 对于参考平面,重要的是过孔的间隙部分不会干扰返回电流的路径。 在障碍物的情况下,返回电流会绕过它。 但是,这样做,电流的电磁场很可能会干扰其他信号迹线的场,从而引入串扰。 此外,这个障碍物会对通过它的走线的阻抗产生不利影响,从而导致不连续性和 EMI 增加。

为了为返回电流提供连续的低阻抗路径,参考平面(电源和接地平面)必须是实心铜片,并且没有空隙和裂缝。 对于参考平面,重要的是过孔的间隙部分不会干扰返回电流的路径。 在障碍物的情况下,返回电流会绕过它。 但是,这样做,电流的电磁场很可能会干扰其他信号迹线的场,从而引入串扰。 此外,这个障碍物会对通过它的走线的阻抗产生不利影响,从而导致不连续性和 EMI 增加。

4.6 路由

4.6 路由

在尝试保持信号完整性、避免噪声拾取和降低 EMI 时,需要制定 PCB 走线和放置组件的指南。 尽管似乎采取了无数的预防措施,但本节仅提供一些主要建议作为布局指导。

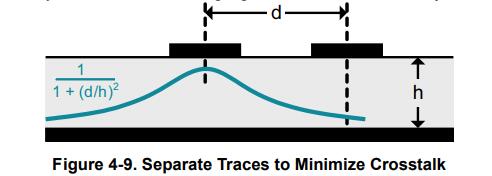

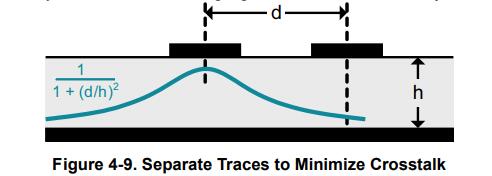

1. 将信号迹线保持 3 倍于迹线到地高度 (d = 3h) 的距离,以将串扰降低至 10%。 因为信号迹线下的返回电流密度通过 1/ [1+(d/h)2] 函数减小,所以它在 d > 3h 点的密度足够小,可以避免在相邻迹线中引起明显的串扰。

2. 使用 45° 折弯(倒角),而不是直角 (90°) 折弯。 直角弯曲增加了有效走线宽度,从而增加了走线阻抗。 这会产生额外的阻抗失配,从而可能导致更高的反射。

2. 使用 45° 折弯(倒角),而不是直角 (90°) 折弯。 直角弯曲增加了有效走线宽度,从而增加了走线阻抗。 这会产生额外的阻抗失配,从而可能导致更高的反射。

3. 为了在嘈杂的环境中永久运行,通过过孔将隔离器的使能输入连接到适当的参考平面,即高使能输入连接到 VCC 平面,低使能输入连接到接地平面。

3. 为了在嘈杂的环境中永久运行,通过过孔将隔离器的使能输入连接到适当的参考平面,即高使能输入连接到 VCC 平面,低使能输入连接到接地平面。

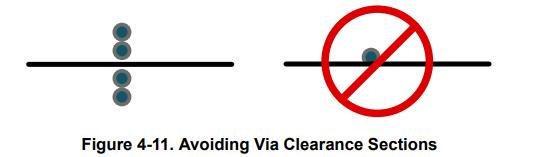

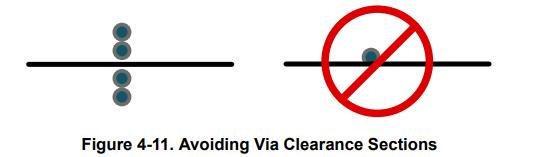

4. 在过孔旁边或过孔阵列之间布线时,确保过孔间隙部分不会中断下方接地层上的返回电流路径。 如果过孔间隙部分位于返回路径中,则返回电流会在其周围找到电感最小的路径。 这样做,它可能会在其他信号迹线下方交叉,从而产生串扰并增加 EMI。

5. 避免使用信号走线改变层,因为这会导致信号路径的电感增加。

5. 避免使用信号走线改变层,因为这会导致信号路径的电感增加。

6. 但是,如果不同层上的信号走线布线不可避免,请为每个信号走线过孔附上一个返回走线过孔。 在这种情况下,请使用尽可能小的通孔尺寸,以将电感的增加保持在最低限度。

7. 使用坚固的电源和接地层进行阻抗控制和最小化电源噪声。

8. 在隔离器和周围电路之间使用较短的走线长度以避免噪声拾取。 数字隔离器通常伴随着隔离的 DC-DC 转换器,通过隔离栅提供电源。 由于单端传输信号对噪声拾取敏感,因此很容易通过长信号迹线拾取附近 DC-DC 转换器的开关频率。

9. 将大容量电容器(即 10 μF)放置在靠近电源(例如稳压器)或向 PCB 供电的地方。

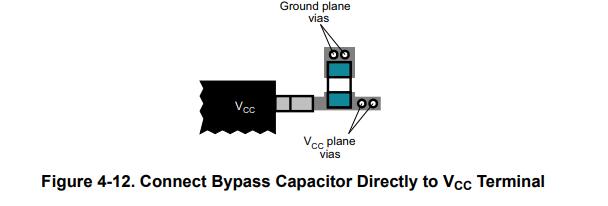

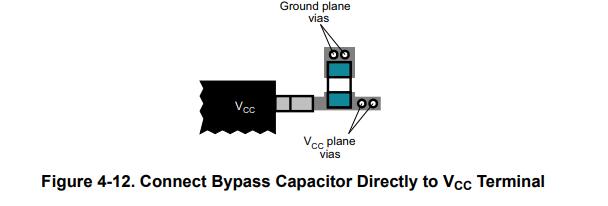

10. 通过将电容器的电源侧直接连接到设备的电源端子并通过两个通孔连接到 Vcc 平面和电容器的接地侧,在设备上放置较小的 0.1-μF 或 0.01-μF 旁路电容器 通过两个通孔到地平面。

4.7 过孔

4.7 过孔

通孔一词通常是指印刷电路板上的电镀孔。 尽管某些应用要求通孔过孔足够宽以容纳通孔元件的引线,但高速板设计主要将其用作更改信号层时的走线过孔,或用作连接过孔以将 SMT 元件连接到所需的 参考平面,也可以将相同电位的参考平面相互连接。

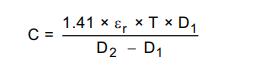

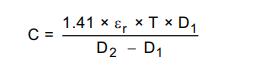

连接到通孔的层通过与通孔周围的焊盘(通孔焊盘)直接接触来实现。 不得连接的层由间隙环隔开。 每个通孔都有一个对地电容,可以使用以下等式近似计算:

在哪里

在哪里

• D2 = 接地层间隙孔的直径,[in.]。

• D1 = 焊盘环绕通孔的直径,[in.]。

• T = 印刷电路板的厚度,[in.]。

• εr = 电路板的介电常数。

• C = 寄生电容,[pF]。

因为电容与尺寸成正比增加,所以高速设计中的走线过孔必须尽可能小,以避免由重电容负载引起的信号衰减。

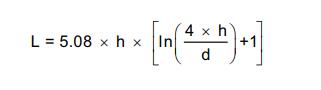

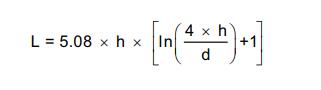

在将去耦电容连接到接地层或互连接地层时,通孔电感变得比其电容更重要。 该电感的大小约为:

在哪里

在哪里

• L = 过孔电感,[nH]。

• h = 通孔长度,[in.]。

• d = 通孔直径,[in.]。

因为这个方程涉及对数,所以改变通孔直径对电感的影响很小。改变通孔长度或并联使用多个通孔可能会影响很大的变化。 因此,通过每个器件端子使用两个并联过孔将去耦电容接地。 对于接地层之间的低电感连接,请在电路板上以规则的间隔使用多个过孔。

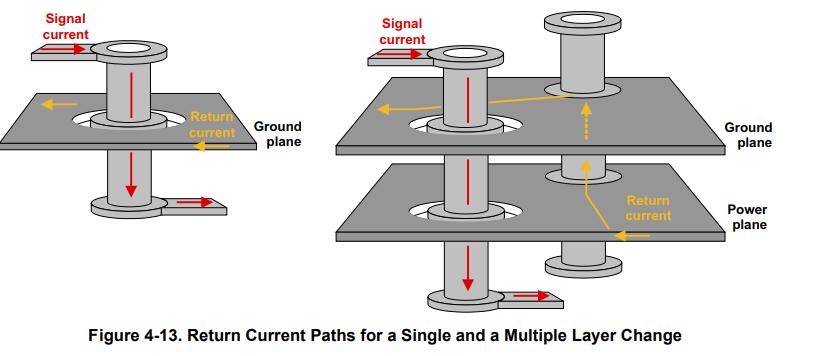

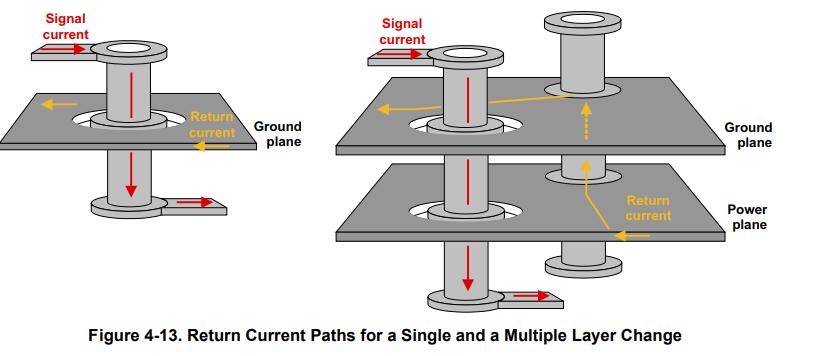

虽然强烈建议不要更改高速走线的层数,但如果仍然需要,请确保连续的返回电流路径。 图 4-13 左侧显示了单层更改的返回电流流向,右侧显示了多层更改的返回电流。

电流从接地平面的底部变化到顶部的能力是由内部间隙环的金属层压板提供的。因此,当信号通过过孔并在同一平面的另一侧继续时,不存在返回电流不连续性。

电流从接地平面的底部变化到顶部的能力是由内部间隙环的金属层压板提供的。因此,当信号通过过孔并在同一平面的另一侧继续时,不存在返回电流不连续性。

通过跨越多个参考平面将信号迹线从一层更改为另一层会使返回电流路径的设计复杂化。在有两个接地层的情况下,必须在信号过孔附近放置一个接地过孔,以确保连续的返回电流路径(图 4-13 中的右图)。

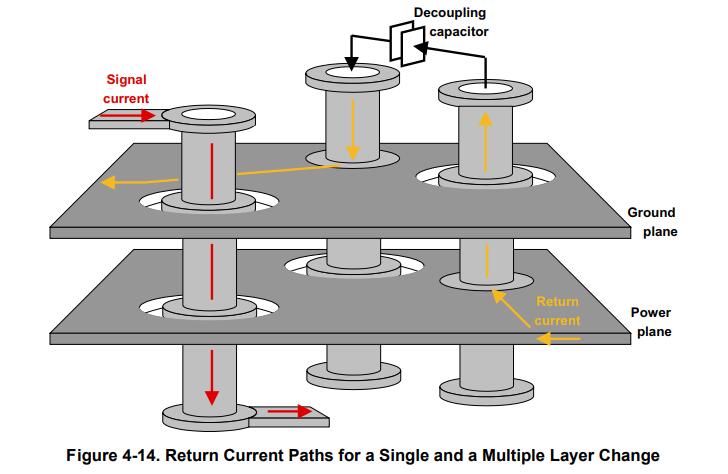

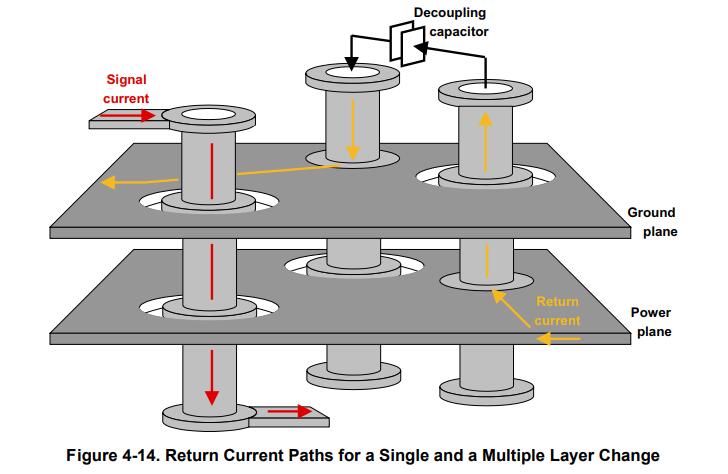

如果参考层具有不同的电压电位,例如图 4-14 中的电源层和接地层,则返回路径的设计会变得混乱,因为它需要第三个通孔和一个去耦电容。返回电流从电源层底部开始,在该底部最接近信号电流。然后它流过电源过孔,穿过去耦电容进入接地过孔,然后返回接地层顶部。

包含多个过孔和去耦电容器的电流返回路径具有高电感,因此会影响信号完整性并增加 EMI。 如果可能,请避免在高速走线布线期间更换层,因为这通常会降低电路板性能、使设计复杂化并增加制造成本。

包含多个过孔和去耦电容器的电流返回路径具有高电感,因此会影响信号完整性并增加 EMI。 如果可能,请避免在高速走线布线期间更换层,因为这通常会降低电路板性能、使设计复杂化并增加制造成本。

4.8 去耦电容

去耦电容器为需要大量电源电流以响应内部开关的 IC 提供本地充电源。去耦不足会导致所需的电源电流不足,这可能会阻止 IC 正常工作,从而导致发生信号完整性数据错误。这要求它们在感兴趣的频率范围内提供低阻抗。为了实现这一点,一种常见的方法是在电路板上均匀分布一组去耦电容器。除了保持信号完整性之外,去耦电容器还充当 EMC 滤波器,防止高频射频信号在整个 PCB 中传播。

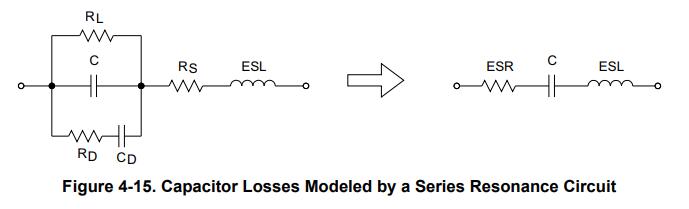

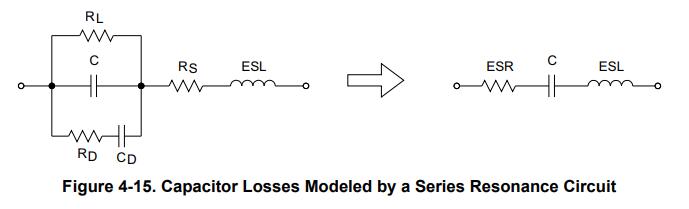

当在电源层和接地层之间连接一个电容器时,电源实际上加载了一个串联谐振电路,其频率相关的 R-L-C 组件代表了一个真实电容器的等效电路。图 4-15 显示了初始等效电路的寄生元件及其转换为串联谐振电路的情况。

漏电阻 RL 代表低频下漏电流的损耗。 RD 和 CD 表示由于分子极化 (RD) 和介电吸收 (CD) 引起的损耗。 RS 描绘了电容器引线和极板中的电阻。 三个电阻损耗合并为一个等效串联电阻 (ESR)。 与 ESR 情况一样,等效串联电感 (ESL) 结合了电容器极板和内部引线的电感。

漏电阻 RL 代表低频下漏电流的损耗。 RD 和 CD 表示由于分子极化 (RD) 和介电吸收 (CD) 引起的损耗。 RS 描绘了电容器引线和极板中的电阻。 三个电阻损耗合并为一个等效串联电阻 (ESR)。 与 ESR 情况一样,等效串联电感 (ESL) 结合了电容器极板和内部引线的电感。

请注意,电容器连接通孔虽然阻抗低,但对串联电感的贡献很大。 因此,通过在每个电容器端子上使用两个过孔来降低过孔电感。

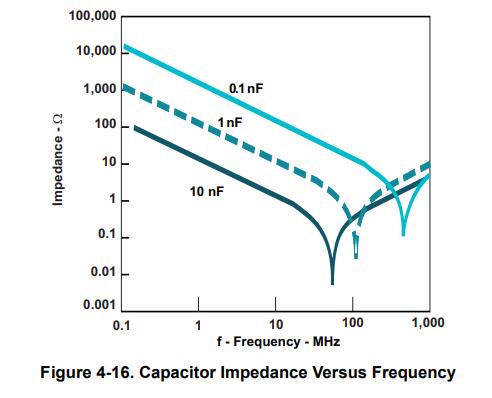

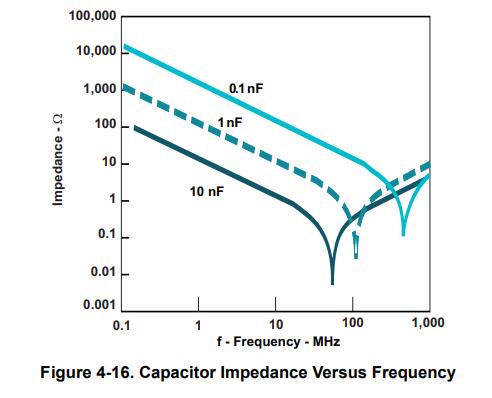

图 4-16 显示了 10nF 电容器的电容器阻抗 (Z) 与频率的关系。 在远低于自谐振频率 (SRF) 的频率下,容抗占主导地位。 更接近 SRF,感抗获得影响试图中和电容分量。 在 SRF 时,容抗和感抗抵消,只有 ESR 有效。 请注意,ESR 与频率有关,并且与普遍的看法相反,在 SRF 时没有达到其最小值。 然而,阻抗 Z 确实如此。

在分布式去耦网络中并联电容器起作用的原因是总电容增加到 CTOT = C × n,其中 n 是使用的去耦电容器的数量。 当 Xc= 1/(ω × C) 时,对于低于 SRF 的频率,电容器阻抗降低到 Xc = 1/(n × ω × C)。 同样,这也适用于电感。 这里 LTOT = L/n,因为 XL = ω × L,对于高于 SRF 的频率,阻抗减小到 XL = ω × L/n。

在分布式去耦网络中并联电容器起作用的原因是总电容增加到 CTOT = C × n,其中 n 是使用的去耦电容器的数量。 当 Xc= 1/(ω × C) 时,对于低于 SRF 的频率,电容器阻抗降低到 Xc = 1/(n × ω × C)。 同样,这也适用于电感。 这里 LTOT = L/n,因为 XL = ω × L,对于高于 SRF 的频率,阻抗减小到 XL = ω × L/n。

设计可靠的去耦网络必须包括低至直流的较低频率,这需要实施大型旁路电容器。 因此,要在低频下提供足够的低阻抗,请在稳压器的输出端和向 PCB 供电的点放置 1-μF 至 10-μF 的钽电容。 对于更高的频率范围,在每个高速开关 IC 旁边放置几个 0.1-μF 或 0.01-μF 陶瓷电容器。

贝博BB官网(中国)有限公司官网是一家专注于光电半导体的代理商和分销商。主要生产光耦继电器,固态继电器,国产光耦,线性,数字隔离器,高速光耦,光电耦合器,光继电器等产品,可为客户提供完善的解决方案。

4.1 PCB材料

对于工作速度低于150 Mbps(或上升和下降时间高于1 ns)且迹线长度高达10英寸的数字电路板,使用标准FR-4环氧玻璃作为印刷电路板(PCB)材料。FR-4(阻燃剂4)符合美国保险商实验室UL94-V0的要求,由于其在高频下较低的介电损耗、较少的吸湿性、较大的强度和刚度,以及其自熄性、易燃性,因此优于较便宜的替代品。

4.2层堆栈

完成低EMI PCB设计至少需要四层(见图4-1)。层堆叠必须按照以下顺序(从上到下):高速信号层、地平面、电源平面和低频信号层。

●在高速信号层旁边放置一个实心接地层,为传输线互连建立受控阻抗,并为回流提供良好的低电感路径。

●将电源板放置在接地层旁边会产生约100 pF/in2的额外高频旁路电容。

●在底层路由较慢的速度控制信号允许更大的灵活性,因为这些信号链路通常有容限来容忍不连续性,如过孔。

如果需要额外的电源电压平面或信号层,请在堆栈中添加第二个电源/接地平面系统以保持对称。 这使得堆栈机械稳定并防止其翘曲。 此外,每个电源系统的电源层和接地层可以放置得更近,从而显着增加高频旁路电容。

4.3爬电距离

爬电距离是沿绝缘表面测量的两个导电部件之间的最短路径。适当的爬电距离可防止跟踪,这是一种由于绝缘表面上或附近的放电而在绝缘材料表面产生局部劣化的部分导电路径的过程。

漏电起痕的程度取决于材料的比较漏电起痕指数(CTI)和环境污染程度。 CTI 用于电绝缘材料,提供在标准测试期间通过跟踪导致失效的电压数值。 IEC 112 对跟踪和 CTI 提供了更全面的解释。

跟踪损坏绝缘材料通常是由于以下一个或多个原因造成的:大气湿度、污染、腐蚀性化学品和设备运行的海拔高度。

随着隔离电压水平的不断升高,拥有一个稳健的PCB设计比以往任何时候都更加重要,该设计不仅可以减少电磁干扰发射,还可以减少爬电问题。除了宽隔离器封装外,还可以使用槽等技术来达到所需的爬电距离(见图4-2)。

此外,在所有层上,保持隔离器下方的空间没有走线、过孔和焊盘,以保持最大爬电距离(见图 4-1)。

4.4受控阻抗传输线

受控阻抗传输线是一条其特性阻抗Z0由迹线几何形状严格控制的迹线。通常,这些迹线与传输介质(如电缆和线路终端)的差分阻抗匹配,以最小化信号反射。在数字隔离器周围,受控阻抗迹线必须与隔离器输出阻抗Z0~rO匹配,这称为源阻抗匹配。

在给定t和εr的情况下,设计师可以通过迹线宽度w和距离d自由定义Z0。然而,对于PCB设计,最关键的尺寸不是w和d的绝对值,而是它们的比值w/d。简化设计师的任务,图4-5绘制了特征迹线阻抗,作为迹线厚度为2.74密耳(2-oz镀铜)、FR-4电介质为4.5以及高于接地层的迹线高度为10密耳时的宽高比(w/h)的函数。

注意,前面的设计示例只是实现所需Z0的多种可能性之一。由于镀铜量较高或较低,或者可以使用不同的PCB材料,所以痕迹厚度不同,但需要改变w/d比。表4-1给出了计算特性阻抗Z0的相当复杂的数学方程,同时考虑了迹线厚度、宽度和电介质。

4.5 数字隔离器参考设计平面

高速 PCB 设计的电源层和接地层通常必须满足各种要求。

在直流和低频下,它们必须向集成电路 (IC) 的电源端子提供稳定的参考电压,例如 VCC 和地。

在高频下,参考平面,特别是接地平面,有多种用途。 对于受控阻抗传输系统的设计,接地层必须提供与相邻信号层的信号迹线的强电耦合。

考虑一个带有相关电场和磁场的单一交流导体,如图 4-6 所示。

松散或无电耦合允许由电流产生的横向电磁 (TEM) 波自由辐射到外部环境中,从而导致严重的电磁干扰 (EMI)。

图 4-7 显示了在接地层和紧密耦合的信号走线之间发生的相同效应。高频电流遵循电感最小的路径,而不是阻抗最小的路径。由于电感最小的返回路径直接位于信号迹线下方,因此返回信号电流往往会沿着这条路径流动。受限的回流电流在接地层中形成了一个高电流密度区域,就在信号迹线的正下方。然后,该接地平面区域充当单个返回迹线,允许磁场抵消,同时为上方的信号迹线提供紧密的电耦合。

在尝试保持信号完整性、避免噪声拾取和降低 EMI 时,需要制定 PCB 走线和放置组件的指南。 尽管似乎采取了无数的预防措施,但本节仅提供一些主要建议作为布局指导。

1. 将信号迹线保持 3 倍于迹线到地高度 (d = 3h) 的距离,以将串扰降低至 10%。 因为信号迹线下的返回电流密度通过 1/ [1+(d/h)2] 函数减小,所以它在 d > 3h 点的密度足够小,可以避免在相邻迹线中引起明显的串扰。

4. 在过孔旁边或过孔阵列之间布线时,确保过孔间隙部分不会中断下方接地层上的返回电流路径。 如果过孔间隙部分位于返回路径中,则返回电流会在其周围找到电感最小的路径。 这样做,它可能会在其他信号迹线下方交叉,从而产生串扰并增加 EMI。

6. 但是,如果不同层上的信号走线布线不可避免,请为每个信号走线过孔附上一个返回走线过孔。 在这种情况下,请使用尽可能小的通孔尺寸,以将电感的增加保持在最低限度。

7. 使用坚固的电源和接地层进行阻抗控制和最小化电源噪声。

8. 在隔离器和周围电路之间使用较短的走线长度以避免噪声拾取。 数字隔离器通常伴随着隔离的 DC-DC 转换器,通过隔离栅提供电源。 由于单端传输信号对噪声拾取敏感,因此很容易通过长信号迹线拾取附近 DC-DC 转换器的开关频率。

9. 将大容量电容器(即 10 μF)放置在靠近电源(例如稳压器)或向 PCB 供电的地方。

10. 通过将电容器的电源侧直接连接到设备的电源端子并通过两个通孔连接到 Vcc 平面和电容器的接地侧,在设备上放置较小的 0.1-μF 或 0.01-μF 旁路电容器 通过两个通孔到地平面。

通孔一词通常是指印刷电路板上的电镀孔。 尽管某些应用要求通孔过孔足够宽以容纳通孔元件的引线,但高速板设计主要将其用作更改信号层时的走线过孔,或用作连接过孔以将 SMT 元件连接到所需的 参考平面,也可以将相同电位的参考平面相互连接。

连接到通孔的层通过与通孔周围的焊盘(通孔焊盘)直接接触来实现。 不得连接的层由间隙环隔开。 每个通孔都有一个对地电容,可以使用以下等式近似计算:

• D2 = 接地层间隙孔的直径,[in.]。

• D1 = 焊盘环绕通孔的直径,[in.]。

• T = 印刷电路板的厚度,[in.]。

• εr = 电路板的介电常数。

• C = 寄生电容,[pF]。

因为电容与尺寸成正比增加,所以高速设计中的走线过孔必须尽可能小,以避免由重电容负载引起的信号衰减。

在将去耦电容连接到接地层或互连接地层时,通孔电感变得比其电容更重要。 该电感的大小约为:

• L = 过孔电感,[nH]。

• h = 通孔长度,[in.]。

• d = 通孔直径,[in.]。

因为这个方程涉及对数,所以改变通孔直径对电感的影响很小。改变通孔长度或并联使用多个通孔可能会影响很大的变化。 因此,通过每个器件端子使用两个并联过孔将去耦电容接地。 对于接地层之间的低电感连接,请在电路板上以规则的间隔使用多个过孔。

虽然强烈建议不要更改高速走线的层数,但如果仍然需要,请确保连续的返回电流路径。 图 4-13 左侧显示了单层更改的返回电流流向,右侧显示了多层更改的返回电流。

通过跨越多个参考平面将信号迹线从一层更改为另一层会使返回电流路径的设计复杂化。在有两个接地层的情况下,必须在信号过孔附近放置一个接地过孔,以确保连续的返回电流路径(图 4-13 中的右图)。

如果参考层具有不同的电压电位,例如图 4-14 中的电源层和接地层,则返回路径的设计会变得混乱,因为它需要第三个通孔和一个去耦电容。返回电流从电源层底部开始,在该底部最接近信号电流。然后它流过电源过孔,穿过去耦电容进入接地过孔,然后返回接地层顶部。

4.8 去耦电容

去耦电容器为需要大量电源电流以响应内部开关的 IC 提供本地充电源。去耦不足会导致所需的电源电流不足,这可能会阻止 IC 正常工作,从而导致发生信号完整性数据错误。这要求它们在感兴趣的频率范围内提供低阻抗。为了实现这一点,一种常见的方法是在电路板上均匀分布一组去耦电容器。除了保持信号完整性之外,去耦电容器还充当 EMC 滤波器,防止高频射频信号在整个 PCB 中传播。

当在电源层和接地层之间连接一个电容器时,电源实际上加载了一个串联谐振电路,其频率相关的 R-L-C 组件代表了一个真实电容器的等效电路。图 4-15 显示了初始等效电路的寄生元件及其转换为串联谐振电路的情况。

请注意,电容器连接通孔虽然阻抗低,但对串联电感的贡献很大。 因此,通过在每个电容器端子上使用两个过孔来降低过孔电感。

图 4-16 显示了 10nF 电容器的电容器阻抗 (Z) 与频率的关系。 在远低于自谐振频率 (SRF) 的频率下,容抗占主导地位。 更接近 SRF,感抗获得影响试图中和电容分量。 在 SRF 时,容抗和感抗抵消,只有 ESR 有效。 请注意,ESR 与频率有关,并且与普遍的看法相反,在 SRF 时没有达到其最小值。 然而,阻抗 Z 确实如此。

设计可靠的去耦网络必须包括低至直流的较低频率,这需要实施大型旁路电容器。 因此,要在低频下提供足够的低阻抗,请在稳压器的输出端和向 PCB 供电的点放置 1-μF 至 10-μF 的钽电容。 对于更高的频率范围,在每个高速开关 IC 旁边放置几个 0.1-μF 或 0.01-μF 陶瓷电容器。

贝博BB官网(中国)有限公司官网是一家专注于光电半导体的代理商和分销商。主要生产光耦继电器,固态继电器,国产光耦,线性,数字隔离器,高速光耦,光电耦合器,光继电器等产品,可为客户提供完善的解决方案。